| 推出年份 | 1985年 |

|---|---|

| 設計公司 | MIPS科技公司→Imagination Technologies |

| 最新架構版本 | MIPS32/64 Release 6(2014) |

| 是否開放架構? | 部分。R12000處理器已經上市20多年,因此不受專利保護。因此,R12000及更早的處理器是完全開放的。 |

| 體系結構類型 | 暫存器-暫存器 |

| 字長/暫存器資料寬度 | 32位元→64位元 |

| 位元組序 | 雙端序 |

| 指令編碼長度 | 固定長度 |

| 指令集架構設計策略 | 精簡指令集(RISC) |

| 擴展指令集 | MDMX、MIPS-3D |

| 分支預測結構 | 比較和分支 |

| 通用暫存器 | 32 |

| 浮點暫存器 | 32 |

| 分頁大小 | 4 KB |

MIPS(Microprocessor without Interlocked Pipeline Stages)[1],是一種採取精簡指令集(RISC)的指令集架構(ISA)[2]:A-1[3]:19,由美國MIPS電腦系統公司開發,現為美普思科技。MIPS廣泛被使用在許多電子產品、網路裝置、個人娛樂裝置與商業裝置上。最早的MIPS架構是32位元,最新的版本已經變成64位元。商業市場主要競爭對手為ARM與RISC-V。

MIPS架構有多個版本,包括MIPS I、II、III、IV,以及MIPS V,它們各是MIPS32/64( 32位元、64位元的實現)發布的五個版本。早期的MIPS架構只有32位元的版本,隨後才開發64位元的版本。截至2017年4月,MIPS32/64的目前版本是MIPS32/64 Release 6[4][5]。MIPS32/64與MIPS I-V的主要區別不僅在於它除了使用者態架構外,還定義了特權核心模式的系統控制協處理器。

MIPS架構有幾個可選的拓展,比如MIPS-3D,它是一個專用於常見3D計算任務的浮點SIMD指令集的簡單集合[6];MDMX(MaDMaX)是一個應用更加廣泛的整數SIMD指令集,它使用了64位元浮點數暫存器;MIPS16e則為提供了指令流壓縮的功能,這可以減小程式的體積[7];MIPS MT則提供了多執行緒的能力[8]。

在一些大學和技術學校中電腦架構的課程上,學生們通常會學習MIPS架構[9]。這個架構極大地影響了後來的精簡指令集架構,如Alpha。2021年3月,MIPS宣布MIPS架構的開發已經結束,因為該公司正在向RISC-V過渡[10]。

歷史

MIPS架構的第一個版本是由MIPS電腦系統公司為其R2000微處理器設計的,這是第一個MIPS的實現。MIPS和R2000都是在1985年一起推出的[來源請求]。當MIPS II推出時,MIPS更名為MIPS I,以區別於新版本[3]:32。

MIPS電腦系統公司的R6000微處理器(1989年)是第一個MIPS II實現[3]:8,專為伺服器設計,由Bipolar Integrated Technology製造和銷售,但在商業上失敗了。在1990年代中期,許多用於嵌入式系統的新32位元MIPS處理器都是MIPS II實現,因為1991年引入64位元MIPS III架構,使得直到1999年MIPS 32推出前,MIPS II都是最新的32位元MIPS架構[3]:19。

MIPS電腦系統公司的R4000微處理器(1991年)是第一個MIPS III實現。它設計用於個人、工作站和伺服器電腦。MIPS電腦系統積極推廣MIPS架構和R4000,建立進階計算環境(ACE)聯盟以推進其進階RISC計算(ARC)標準,旨在將MIPS建立為主導的個人計算平台。ARC在個人電腦上幾乎沒有成功,但R4000(和R4400衍生產品)廣泛用於工作站和伺服器電腦,尤其是其最大的使用者矽谷圖形公司(SGI)。R4000的其他用途包括高階嵌入式系統和超級電腦。MIPS III最終由許多嵌入式微處理器實現。Quantum Effect Design的R4600(1993年)及其衍生產品廣泛應用於高階嵌入式系統和低階工作站和伺服器。MIPS科技的R4200(1994年)專為嵌入式系統、筆記型電腦和個人電腦而設計。NEC製造的衍生產品R4300i用於N64遊戲機。N64和PlayStation是1990年代中期MIPS架構處理器的最大使用者之一。

第一個MIPS IV實現是MIPS科技R8000微處理器晶片組(1994年)。R8000的設計始於矽谷圖形公司,它僅用於高階工作站和伺服器,用於高效能浮點工作負載關鍵的科學和技術應用。後來的實現是MIPS科技的R10000(1996年),Quantum Effect Devices的R5000(1996年)和RM7000(1998年)。NEC和東芝製造和銷售的R10000及其衍生產品被NEC、Pyramid Technology、SGI和Tandem Computers(以及其他公司)用於工作站、伺服器和超級電腦。R5000和R7000可用於高階嵌入式系統、個人電腦以及低階工作站和伺服器。東芝R5000的衍生產品R5900用於索尼的Emotion Engine,該引擎為其PlayStation 2遊戲機提供動力。

MIPS V於1996年10月21日在微處理器論壇上與MIPS數位媒體擴充(MDMX)擴充一起發布,旨在提高3D圖形變換的效能[11]。在1990年代中期,非嵌入式MIPS微處理器的主要用途是SGI的圖形工作站。MIPS V使用僅整數的MDMX擴充,以此提高3D圖形應用程式的效能[12]。MIPS V從未真正實現。1997年5月12日,SGI發布了「H1」(「野獸」)和「H2」(「船長」)微處理器。前者計劃是第一個MIPS V實現,預計於1999年上半年推出[13]。「H1」和「H2」專案後來合併,最終在1998年取消。雖然沒有任何MIPS V實現,但MIPS64 Release 1(1999年)基於MIPS V並保留其所有功能作為可選的協處理器1(FPU)功能,稱為配對單精度(Paired-Single)。

當MIPS科技公司於1998年從SGI分拆出來時,它重新專注於嵌入式市場。直到MIPS V,每個後續版本都是前一個版本的嚴格超集,但是發現這是一個問題[來源請求],隨後架構更改為分別定義32位元和64位元:MIPS32和MIPS64。兩者都於1999年推出[14]。MIPS32基於MIPS II,,並帶有MIPS III、MIPS IV和MIPS V的一些附加特性;MIPS64基於MIPS V[14]。NEC、東芝和SiByte(後來被博通收購)在MIPS64發布後都獲得了許可證。飛利浦、LSI Logic、IDT、Raza Microelectronics, Inc.、凱為、龍芯和君正已加入其中。MIPS32/MIPS64 Release 5於2012年12月6日發布[15]。第4版被跳過,因為在許多亞洲文化中,數字4被認為是不吉利的[16]。

2018年6月—美國矽谷新創AI晶片公司Wave Computing宣佈完成收購MIPS公司股權,MIPS公司維持獨立運作,並預計開源MIPS架構[17]。

2018年12月,MIPS架構的新所有者Wave Computing宣布MIPS ISA將在一個名為MIPS開放計劃的專案中開源[18]。該計劃旨在開放對32位元和64位元設計的最新版本的存取,使其無需任何許可或版稅即可使用,並授予參與者現有MIPS專利的許可[19][20][21]。

2019年3月,該架構的一個版本在免版稅許可下可用[22],但該年晚些時候該程式再次關閉[23]。

2021年3月,WaveComputing宣布停止MIPS架構的開發。該公司已加入RISC-V基金會,未來的處理器設計將基於RISC-V架構[24][25]。

設計

MIPS是一種模組化架構,最多支援四個協處理器(CP0/1/2/3)。在MIPS術語中,CP0是系統控制協處理器(MIPS I-V中處理器的重要部分,與實現相關),CP1是可選的浮點運算器(FPU),CP2/3是可選的由實現定義的協處理器(MIPS III刪除了CP3並將其操作碼重新用於其他目的)。例如,在PlayStation電動遊戲機中,CP2是幾何變換引擎(GTE),它可以加速3D電腦圖形中的幾何處理。

版本

MIPS I

MIPS是一種載入-儲存架構(也稱為暫存器-暫存器架構);除了用於存取電腦記憶體的載入/儲存指令外,所有指令都對暫存器進行操作。

暫存器

MIPS I有32個32位元通用暫存器(GPR)。暫存器$0寫死為零,寫入的內容將被丟棄。暫存器$31是連結暫存器。對於與其他指令非同步執行的整數乘法和除法指令,提供了一對32位元暫存器HI和LO。有一小組指令用於在通用暫存器和HI/LO暫存器之間複製資料。

程式計數器(PC)有32位元。低二位總是為零,因為MIPS I指令有32位元長,並且與它們的自然字邊界對齊。

指令格式

指令分為三種類型:R型(Register)、I型(Immediate )和J型(Jump)。三種類型的指令的最高6位均為6位的opcode碼。從25位往下,

- R型指令用連續三個5位二進位碼來表示三個暫存器的位址,然後用一個5位二進位碼來表示移位的位數(如果未使用移位元運算,則全為0),最後為6位的function碼(它與opcode碼共同決定R型指令的具體操作方式);

- I型指令則用連續兩個5位二進位碼來表示兩個暫存器的位址,然後是一個16位元二進位碼來表示的一個立即數二進位碼;

- J型指令用26位二進位碼來表示跳轉目標的指令位址(實際的指令位址應為32位元,其中最低兩位為00)。[26][27]

三種用於核心指令集的指令圖示如下:

| 類型 | 位 | |||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| R | opcode (6) | rs (5) | rt (5) | rd (5) | shamt (5) | funct (6) | ||||||||||||||||||||||||||

| I | opcode (6) | rs (5) | rt (5) | immediate (16) | ||||||||||||||||||||||||||||

| J | opcode (6) | address (26) | ||||||||||||||||||||||||||||||

CPU指令

MIPS I有載入和儲存8位元的位元組、16位元的半字和32位元的字的指令。僅支援一種定址模式:基址+位移。由於MIPS I是32位元架構,因此載入少於32位元的值需要將資料有符號或無符號擴充到32位元。以「unsigned」為字尾的載入指令執行無符號擴充;否則執行有符號擴充。載入指令從GPR(rs)的內容中取得基址,並將結果寫入另一個GPR(rt)。儲存指令從GPR(rs)的內容中取得基址,從另一個GPR(rt)取得儲存資料。所有載入和儲存指令都通過將基址與符號擴充的16位元立即數相加來計算記憶體位址。MIPS I要求所有記憶體存取都與其自然字邊界對齊,否則會發出異常訊號。「左」或「右」為字尾的載入/儲存字指令用以支援高效的未對齊記憶體存取。所有載入指令後都有一條指令的載入延遲槽。載入延遲槽中的指令不能使用載入指令載入的資料。載入延遲槽可以填充一條不依賴於載入的指令;如果找不到這樣的指令,則用nop代替。

MIPS I有執行加法和減法的指令。這些指令從兩個GPR(rs和rt)取得它們的運算元,並將結果寫入第三個GPR(rd)。此外,加法可以從16位元立即數(有符號擴充為32位元)中取得運算元之一。加減法指令有兩種變體:預設情況下,如果結果溢位則發出異常訊號;帶有「unsigned」字尾的指令不會發出異常訊號。溢位檢查將結果解釋為32位元二補數整數。MIPS I有執行按位元邏輯AND、OR、XOR和NOR的指令。這些指令從兩個GPR取得其運算元並將結果寫入第三個GPR。AND、OR和XOR指令也可以從16位元立即數(無符號擴充到32位元)中取得運算元之一。如果指定的關係為真或假,則Seton關係指令將1或0寫入目標暫存器。這些指令的運算元來自兩個GPR或一個GPR和一個16位元立即數(符號擴充為32位元),並將結果寫入第三個GPR。預設情況下,運算元被解釋為有符號整數。以「unsigned」為字尾的指令的變體將運算元解釋為無符號整數(即使是對於來自有符號擴充16位元立即數的運算元)。

Load Immediate Upper指令將16位元立即數複製到GPR的高16位元。它與Or Immediate指令結合使用以將32位元立即數載入到暫存器中。

MIPS I有執行左右邏輯移位和右算術移位的指令。運算元從一個GPR(rt)中獲得,並將結果寫入另一個GPR(rd)。位移距離是從GPR(rs)或5位「位移量」(「sa」欄位)中獲得的。

MIPS I有有符號和無符號整數乘法和除法的指令。這些指令從兩個GPR取得其運算元,並將其結果寫入一對稱為HI和LO的32位元暫存器,因為它們可能與其他CPU指令分開(並同時)執行。對於乘法,64位元乘積的高位和低位分別寫入HI和LO。對於除法,商寫入LO,餘數寫入HI。為了存取結果,提供了一對指令(從HI移動和從LO移動)將HI或LO的內容複製到GPR。這些指令是互鎖的:對HI和LO的讀取不會越過未完成的要寫入HI和LO的算術指令。另一對指令(Move to HI或Move to LO)將GPR的內容複製到HI和LO。這些指令用於在例外處理後將HI和LO恢復到其原始狀態。讀取HI或LO的指令必須由不寫入HI或LO的兩條指令分隔。

所有MIPS I控制流指令後需要接一個分支延遲槽。除非分支延遲槽用執行有用工作的指令填充,否則要使用nop。MIPS I分支指令將GPR(rs)的內容與零或另一個GPR(rt)的內容作為有符號整數進行比較,如果指定的條件為真,則跳轉分支。執行位置將轉移到通過將16位元偏移量左移兩位、對18位元結果進行有符號擴充,並將32位元符號擴充結果與程式計數器(指令位址)和810作和得到。跳轉有兩個版本:絕對跳轉和暫存器間接跳轉。絕對跳轉(「Jump」和「Jump and Link」)通過將26位instr_index左移兩位,並將28位元結果與分支延遲槽指令的指令位址高四位連接來計算跳轉的位址。暫存器間接跳轉將控制轉移到來自GPR(rs)的位址處的指令。來自GPR的位址必須是字對齊的,否則在執行分支延遲槽中的指令後會發出異常訊號。連結的分支和跳轉指令(「Jump and Link Register」除外)將返回位址儲存到GPR 31。「Jump and Link Register」指令允許將返回位址儲存到任何可寫的GPR。

MIPS I有兩條軟體用於發出異常訊號的指令:System Call和Breakpoint。System Call被使用者態軟體用來進行核心呼叫;Breakpoint用於核心例外處理程式轉移控制到除錯器。兩條指令都有一個20位的代碼(Code)欄位,可儲存給例外處理程式的操作環境特定資訊。

MIPS有32個浮點暫存器。兩兩暫存器配對用於雙精度數。奇數號暫存器不能用於算術或分支,只是作為雙精度暫存器對的一部分,導致大多數指令只有16個可用暫存器(移動/複製和載入/儲存不受影響)。

單精度指令由.s字尾表示,而雙精度由.d字尾表示。

MIPS II

MIPS II移除了載入延遲槽[3]:41並添加了幾組指令。對於共享記憶體多處理,添加了「Synchronize Shared Memory」、「Load Linked Word」和「Store Conditional Word」指令。添加了一組Trap-on-Condition指令。如果求值為真,這些指令將導致異常。所有現有的分支指令都有了「可能」分支的版本,僅在分支跳轉要執行時才執行分支延遲槽中執行指令[3]:40。在某些情況下,這些指令允許用有用的指令填充分支延遲槽,以此提高效能[3]:212。為COP1-3添加了雙字載入和儲存指令。與其他記憶體存取指令一致,這些載入和儲存要求雙字自然對齊。

浮點協處理器指令集也添加了幾條指令。添加了符合IEEE 754的浮點平方根指令。它支援單精度和雙精度運算元。添加了一組將單精度和雙精度浮點數轉換為32位元字的指令。它們補充了現有的轉換指令,允許用指令控制IEEE捨入模式,而不是通過浮點控制和狀態(Floating Point Control and Status)暫存器。

MIPS III

MIPS III是向下相容MIPS II的擴充,增加了對64位元記憶體定址和整數運算的支援。64位元資料類型稱為雙字,MIPS III將通用暫存器、HI/LO暫存器和程式計數器擴充到64位元以支援。添加了新指令來載入和儲存雙字,對它們執行整數加、減、乘、除和移位元運算,以及在GPR和HI/LO暫存器之間移動雙字。必要時,現有最初定義為對32位元字進行操作的指令被重新定義,以對32位元結果進行符號擴充,使得大多數指令對字和雙字進行的處理行為相同。在這些重新定義的指令中包括「Load Word」。在MIPS III中,它將字有符號擴充到64位元。為了補充「Load Word」,添加了一個無符號擴充版本。

R指令格式無法指定完整的64位元位移距離(其5位位移量欄位太窄,無法指定雙字的位移距離),MIPS III對於每個MIPS I的位移指令,提供了三個64位元的版本。第一個版本是原始移位指令的64位元版本,用於指定介於0-31位元之間的常數位移距離。第二個版本與第一個版本類似,但將位移量欄位的值加上3210,以便可以指定32-64位元之間的常數位移距離。第三個版本從GPR的六個低位取得位移距離。

MIPS III在現有核心和使用者權限級別之間添加了一個「管理員」權限級別。此功能僅影響由實現定義的系統控制處理器(協處理器0)。

MIPS III移除了協處理器3(CP3)相關支援指令,並為新的雙字指令重新使用了其操作碼。其餘的協處理器獲得了在協處理器暫存器和GPR之間移動雙字的指令。浮點通用暫存器(FGR)擴充到64位元,並且取消了指令僅使用偶數暫存器的要求。這與早期版本的架構不相容;浮點控制/狀態暫存器中的一位用於在MIPS I和II相容模式下操作MIPS III浮點單元(FPU)。浮點控制暫存器沒有為相容性進行擴充。添加的唯一新浮點指令是在CPU和FPU之間複製雙字的指令,將單精度和雙精度浮點數轉換為雙字整數,反之亦然。

MIPS IV

MIPS IV是該架構的第四個版本。它是MIPS III的超集,與MIPS的所有現有版本相容。MIPS IV主要旨在提高浮點(FP)效能。為了改進對運算元的存取,添加了用於FP載入和儲存的索引定址模式(基址+索引,均來自GPR),以及用於執行記憶體預取和指定快取提示的預取指令(這些指令同時支援基址+偏移量和基址+索引定址模式)。

MIPS IV添加了幾個特性來改進指令級並列性。為了緩解由單個條件位引起的瓶頸,在浮點控制和狀態暫存器中添加了七個條件代碼位,使總數達到八個。重新定義了FP比較和分支指令,以便它們可(分別)指定寫入或讀取哪個條件位;並且刪除了FP比較與讀取由比較指令寫入條件位的FP分支之間的延遲槽。通過GPR和FPR條件移動指令的形式部分添加了對分支預測的支援;並且實現可以選擇為IEEE 754陷阱提供精確或不精確的例外。

MIPS IV為單精度和雙精度浮點數添加了幾個新的浮點算術指令:融合乘加減、倒數和倒數平方根。FP融合乘加減指令執行一次或兩次捨入(由實現定義),(分別)超過或達到IEEE 754精度要求。FP倒數和倒數平方根指令不符合IEEE 754精度要求,並且產生的結果與所需精度相差一到兩個單位(它是實現定義的)。這些指令服務於指令延遲比準確性更重要的應用程式。

MIPS V

MIPS V添加了一種新的資料類型,配對單精度(PS),它由兩個單精度(32位元)浮點陣列成,儲存在現有的64位元浮點暫存器中。添加了現有算術、比較和條件移動浮點指令的變體,以便以SIMD方式對這種資料類型進行操作。添加了用於載入、重排和轉換PS資料的新指令[3]:426–429。這是第一個利用現有資源實現的浮點SIMD指令集[12]。

MIPS32/MIPS64

MIPS32的第一個版本基於MIPS II,添加了來自R4000和R5000系列64位元處理器的條件移動、預取指令和其他特性[14]。MIPS64的第一個版本增加了一個MIPS32模式來執行32位元代碼[14]。向MIPS32和MIPS64規範添加了以前在某些實現中可用的MUL和MADD(乘加)指令,同樣的還有快取控制指令[14]。

2014年的MIPS32/MIPS64 Release 6添加了以下內容:[28]

- 一個沒有延遲槽的新分支家族:

- 具有26位偏移量的無條件分支(BC)和分支連結(BALC),

- 具有21位偏移量的零/非零條件分支,

- 全套有符號和無符號條件分支,可比較兩個暫存器(例如BGTUC)或一個暫存器與零(例如BGTZC),

- 全套分支和連結,將暫存器與零進行比較(例如BGTZALC)。

- 無延遲槽的索引跳轉指令,旨在支援大絕對位址。

- 在第16、32或48位元處載入16位元立即數的指令,允許輕鬆生成大常數。

- PC相關載入指令,以及大(PC相關)偏移量的位址生成。

- 位反轉和位元組對齊指令(以前僅適用於DSP擴充)。

- 乘法和除法指令重新定義,向單個暫存器輸出結果。

- 生成真值的指令現在生成全零或全一,而不僅僅是清除/設定0位,

- 使用真值的指令現在只將全零解釋為假,而不是只看0位。

刪除了不常用的指令:

- 一些條件移動

- 「可能」分支指令(在以前的版本中已棄用)。

- 具有16位元立即數的整數溢位擷取指令

- 整數累加器指令(連同HI/LO暫存器,移至DSP特定應用擴充)

- 未對齊的載入指令(LWL和LWR)(現要求大多數一般載入和儲存指令支援未對齊的存取,通過陷阱或添加新指令(BALIGN)等形式)

重新組織指令編碼,為未來的擴充騰出空間。

microMIPS

microMIPS32/64架構(分別)是MIPS32和MIPS64架構的超集,旨在取代MIPS16e ASE。MIPS16e的一個缺點是在處理任何16位元指令之前需要切換模式。microMIPS將最常用的32位元指令編碼為16位元指令版本。允許程式混合16位元和32位元指令而無需切換模式。microMIPS與MIPS32/64 Release 3一起推出,MIPS32/64的每個後續版本都有相應的microMIPS32/64版本。處理器可以單獨實現microMIPS32/64,或同時實現microMIPS32/64及其相應的MIPS32/64子集。從MIPS32/64 Release 6開始,對MIPS16e的支援結束,microMIPS是MIPS中唯一的代碼壓縮形式。

應用程式特定擴充

基本的MIPS32和MIPS64架構可以補充一些可選的架構擴充,這些擴充統稱為「應用程式特定擴充」(ASE)。這些ASE提供的功能可以提高某些工作負載的效率和效能,例如數位訊號處理。

- MIPS單晶片

- 微控制器應用的增強功能。MCU ASE(特定應用擴充)用於擴充中斷控制器支援、減少中斷延遲並增強微控制器系統設計中通常需要的I/O外設控制功能。

- 單獨的優先級和向量生成

- 在EIC(外部中斷控制器)模式下支援多達256個中斷和8個硬體中斷引腳

- 提供16位元向量偏移位址

- 中斷異常向量預取

- 自動中斷序言——添加硬體以在中斷處理常式之前儲存和更新系統狀態

- 自動中斷尾聲——恢復先前儲存在堆疊中的系統狀態,以便從中斷返回。

- 中斷鏈——支援掛起中斷的服務,無需登出初始中斷常式,節省儲存和恢復多個活動中斷所需的周期

- 支援推測性預取中斷向量位址。通過將記憶體存取與管道重新整理和異常優先級重疊來減少中斷服務周期數

- 原子性位設定/清除指令,通常可在不中斷的情況下修改I/O暫存器中用於監視或控制外部外圍功能的位,確保安全地執行操作。

- MIPS16

- MIPS16是從MIPS I到V的特定應用擴充,由LSI Logic和MIPS科技設計,於1996年10月21日與其第一個實現LSI Logic TinyRISC處理器一起發布[29]。隨後NEC電子、飛利浦半導體、東芝以及其他公司獲得了MIPS16的許可,並作為MIPS I、II、III架構的擴充實現。MIPS16使用16位元指令而不是32位元指令,減少應用程式的大小多達40%,並且還提高了電源效率、指令快取命中率,並且在效能方面與其基礎架構相當[30]。它由MIPS科技和其他供應商的硬體和軟體開發工具提供支援。MIPS16e是MIPS16的改進版本,首先由MIPS32和MIPS64 Release 1支援。MIPS16e2是MIPS16的改進版本,由MIPS32和MIPS64(直到Release 5)支援。Release 6將其替換為microMIPS。

- MIPS數位訊號處理(DSP)

- DSP ASE是MIPS32/MIPS64 Release 2及更新指令集版本的可選擴充,可用於加速大量「媒體」計算——尤其是音影片。DSP模組包含整數管線中的一組指令和狀態,並且在MIPS處理器核心中實現所需的附加邏輯最少。ASE修訂版2於2006年下半年推出。該修訂版向原始ASE添加了額外的指令,但在其他方面與它向下相容[31]。與MIPS架構的大部分不同,它是一組相當不規則的操作,其中許多是為了某些關鍵演算法特別選擇的。其主要新穎特點(對比原始MIPS32)[32]:

- 飽和算術(當計算溢位時,提供最接近非溢位答案的可表示數字)。

- 有符號32位元和16位元定點小數的定點運算,範圍為-1到+1(廣泛稱為「Q31」和「Q15」)。

- 現有的整數乘法與乘法累加指令,將結果傳送到雙倍大小的累加器(在MIPS32 CPU上稱為「hi/lo」和64位元)。DSP ASE增加了三個累加器,以及一些不同風格的乘法累加。

- SIMD指令在4x無符號位元組或2x16位元值上執行,這些值打包到一個32位元暫存器(DSP ASE的64位元變體也支援更大的向量)。

- SIMD操作是基本算術、移位和一些乘法累加類型的操作。

- MIPS SIMD架構(MSA)

- 旨在加速多媒體的指令集擴充。

- 32個16x8位元、8x16位元、4x32位元和2x64位元向量元素的向量暫存器

- 高效的整數、定點和浮點數向量並列算術運算

- 對絕對值運算元的操作

- 可用的捨入和飽和選項

- 全精度乘法和乘加

- 整數、浮點和定點資料之間的轉換

- 完整的向量級比較和分支指令集,無條件標誌

- 向量(1D)和陣列(2D)打散操作

- 位元組序無關的有類型載入和儲存指令

- 符合IEEE 754-2008浮點運算標準

- 基本精確浮點異常訊號

- 用於有更多門/電晶體的晶片的預定義可延伸擴充

- 結合通用編譯器加速計算密集型應用程式

- 用於消費電子應用或專用硬體未涵蓋的功能的軟體可程式化解決方案

- 新興的資料探勘、特徵提取、圖像和影片處理以及人機互動應用

- 高效能科學計算

- MIPS虛擬化

- 硬體支援的虛擬化技術。

- MIPS多執行緒

- 每個多執行緒MIPS核心最多可以支援兩個VPE(虛擬處理元素),它們共享單個管道以及其他硬體資源。但是,由於每個VPE都包含軟體系統所看到的處理器狀態的完整副本,因此每個VPE對於SMP Linux作業系統來說都是一個完整的獨立處理器。對於更細粒度的執行緒處理應用程式,每個VPE能夠支援多達9個跨兩個VPE分配的TC。TC共享一個公共執行單元,但每個都有自己的程式計數器和核心暫存器檔案,因此每個都可以處理來自軟體的執行緒。MIPS MT架構還允許將處理器周期分配給執行緒,並使用可選的服務品質(QoS)管理塊設定相關執行緒的優先級。這樣有兩個決定跨匯流排資訊流的優先級機制。第一種機制允許使用者優先一個執行緒於另一個執行緒。第二種機制用於隨時間將指定比例的周期分配給特定執行緒。兩種機制的結合使用允許向執行緒集有效分配頻寬,並更好地控制延遲。在即時系統中,系統級確定性非常重要,而QoS塊有助於提高系統的可預測性。進階系統的硬體設計人員可以用專門針對其應用進行調整的模組來替換MIPS科技提供的標準QoS模組。

- SmartMIPS

- SmartMIPS是由Gemplus International和MIPS科技設計的特定於應用程式的擴充(ASE),旨在提高智慧卡軟體的效能並減少記憶體消耗。它僅受MIPS32支援,因為智慧卡不需要MIPS64處理器的功能。很少有智慧卡使用SmartMIPS。

- MIPS數位媒體擴充(MDMX)

- 1990年代常見於RISC和CISC系統上的多媒體應用程式加速。

- MIPS-3D

- 提高3D圖形應用程式效能的附加指令

呼叫約定

MIPS有幾個呼叫約定,尤其是在32位元平台上。

O32 ABI是最常用的ABI,因為它是MIPS的原始System V ABI[33][34]。它嚴格基於堆疊,只有四個暫存器$a0-$a3可用於傳遞參數。堆疊上的空間是保留的,以防被呼叫者需要儲存其參數,但呼叫者不會將暫存器儲存在那裡。返回值儲存在暫存器$v0中;第二個返回值可以儲存在$v1中。ABI形成於1990年,最後一次更新是在1994年。這種肉眼可見的緩慢,以及只有16個暫存器的老式浮點模型,促進了許多其他呼叫約定的擴散。它僅針對32位元MIPS定義,但GCC建立了一個名為O64的64位元變體[35]。

對64位元,最常用的是SGI的N64 ABI。最重要的改進是現有八個暫存器可用於參數傳遞;它還將浮點暫存器的數量增加到32個。還有一個稱為N32的ILP32版本,它使用32位元指標來處理較小的代碼,類似於x32 ABI。兩者都在CPU的64位元模式下執行[35]。N32和N64 ABI將前八個參數傳遞給暫存器$a0-$a7中的函式;後續參數在堆疊上傳遞。返回值(或指向它的指標)儲存在暫存器$v0中;第二個返回值可以儲存在$v1中。在N32和N64 ABI中,所有暫存器都被認為是64位元寬。

已有一些嘗試,使用更類似於N32的32位元ABI替換O32。1995年的一次會議提出了MIPS EABI,其32位元版本非常相似[36]。EABI啟發MIPS科技提出更激進的「NUBI」ABI,重用參數暫存器作為返回值[37]。GCC支援MIPS EABI,但LLVM不支援,兩者也不支援NUBI。

對於O32及N32/N64,返回位址儲存在$ra暫存器中。這是使用JAL(跳轉和連結)或JALR(跳轉和連結暫存器)指令自動設定的。(非葉子)MIPS次常式的函式序言將返回位址(在$ra中)推入堆疊[38][39]。

在O32和N32/N64上,堆疊向下增長,但N32/N64 ABI需要所有堆疊條目64位元對齊。影格指標($30)是可選的,實際上很少使用,除非需要在執行時確定函式中的堆疊分配,例如呼叫了alloca()。

對於N32和N64,返回位址通常儲存在棧指標之前的8個位元組,儘管這可能是可選的。

對於N32和N64 ABI,函式必須保留$S0-$s7暫存器、全域指標($gp或$28)、棧指標($sp或$29)和影格指標($30)。O32 ABI相同,只是$gp暫存器需要由呼叫函式儲存而不是被呼叫函式。

對於多執行緒代碼,執行緒本地儲存指標通常儲存在特殊硬體暫存器$29中,並通過使用mfhw(從硬體移動)指令存取。已知至少有一個供應商將此資訊儲存在$k0暫存器中,該暫存器通常保留供核心使用,但這不是標準的。

$k0和$k1暫存器($26-$27)保留供核心使用,不應由應用程式使用,因為核心可以隨時由於中斷、上下文交換或其他事件而更改這些暫存器。

| 名稱 | 編號 | 用途 | 被調保留? |

|---|---|---|---|

| $zero | $0 | 常數0 | 不適用 |

| $at | $1 | 組譯臨時用 | 否 |

| $v0–$v1 | $2–$3 | 函式返回值和表達式求值 | 否 |

| $a0–$a3 | $4–$7 | 函式參數 | 否 |

| $t0–$t7 | $8–$15 | 臨時 | 否 |

| $s0–$s7 | $16–$23 | 臨時儲存值 | 是 |

| $t8–$t9 | $24–$25 | 臨時 | 否 |

| $k0–$k1 | $26–$27 | 保留核心用 | 不適用 |

| $gp | $28 | 全域指標 | 是(除PIC代碼) |

| $sp | $29 | 棧指標 | 是 |

| $fp | $30 | 影格指標 | 是 |

| $ra | $31 | 返回位址 | 不適用 |

| 名稱 | 編號 | 用途 | 被調保留? |

|---|---|---|---|

| $zero | $0 | 常數0 | 不適用 |

| $at | $1 | 組譯臨時用 | 否 |

| $v0–$v1 | $2–$3 | 函式返回值和表達式求值 | 否 |

| $a0–$a7 | $4–$11 | 函式參數 | 否 |

| $t4–$t7 | $12–$15 | 臨時 | 否 |

| $s0–$s7 | $16–$23 | 臨時儲存值 | 是 |

| $t8–$t9 | $24–$25 | 臨時 | 否 |

| $k0–$k1 | $26–$27 | 保留核心用 | 不適用 |

| $gp | $28 | 全域指標 | 是 |

| $sp | $29 | 棧指標 | 是 |

| $fp | $30 | 影格指標 | 是 |

| $ra | $31 | 返回位址 | 不適用 |

跨呼叫保留的暫存器是(按照約定)不會被系統呼叫或過程(函式)呼叫更改的暫存器。例如,$s-暫存器必須由需要使用它們的過程儲存到堆疊中,而$sp和$fp總是按常數遞增,並在過程完成後遞減(以及它們指向的記憶體)。相比之下,$ra由任何普通函式呼叫(使用jal的函式呼叫)自動更改,並且$t-暫存器必須在任何過程呼叫之前由程式儲存(如果程式在呼叫後需要其中的值)。

Linux上位置無關代碼的使用者空間呼叫約定還要求,當呼叫函式時,$t9暫存器必須包含該函式的位址[41]。這個約定可以追溯到MIPS的System V ABI補充規定[42]。

用途

MIPS處理器用於嵌入式系統,例如住宅閘道器和路由器。最初,MIPS是為通用計算而設計的。在1980年代和1990年代,許多公司在個人、工作站和伺服器電腦上使用MIPS處理器,例如DEC、MIPS Computer Systems、NEC、Pyramid Technology、SiCortex、Siemens Nixdorf、SGI,和Tandem Computers.

從歷史上看,N64、索尼PlayStation、PlayStation 2和PlayStation Portable等電動遊戲機都使用MIPS處理器。MIPS處理器在1990年代也曾在超級電腦中流行,但所有此類系統都從TOP500名單中掉了下來。這些用途最初由嵌入式應用程式補充,但在1990年代,MIPS成為嵌入式處理器市場的主流選擇,到2000年代,大多數MIPS處理器都用於這類應用。

在1990年代中後期,據估計生產的RISC微處理器中有三分之一是MIPS處理器[43]。

到2010年代後期,MIPS機器仍然普遍用於嵌入式市場,包括汽車、無線路由器、LTE數據機(主要為聯發科)和微控制器(例如PIC32M)。它們大多已淡出個人、伺服器和應用領域。

模擬器

開放虛擬平台(OVP)[44]包括可免費用於非商業用途的模擬器OVPsim、處理器模型庫、外圍裝置和平台,以及使使用者能夠開發自己的模型的API。庫中的模型是用C語言編寫的開源模型,包括MIPS4K、24K、34K、74K、1004K、1074K、M14K、microAptiv、interAptiv、proAptiv 32位元核心和MIPS64位元5K系列核心.這些模型由Imperas[45]建立和維護,並與MIPS技術公司合作進行了測試,並得到了MIPS驗證標記。基於MIPS的範例平台包括裸機環境和用於引導未修改的Linux二進位映像的平台。這些平台模擬器可作為原始碼或二進位檔案使用,速度快,非商業用途免費,並且易於使用。OVPsim由Imperas開發和維護,速度非常快(每秒數億條指令),旨在處理多核同構和異構架構和系統。

有一個免費的MIPS32模擬器(早期版本僅類比R2000/R3000)稱為SPIM,用於教育。EduMIPS64[46]是一個GPL圖形跨平台MIPS64CPU模擬器,用Java/Swing編寫。它支援MIPS64 ISA的較大子集,並允許使用者以圖形方式檢視CPU執行組譯程式時管線中發生的情況。

MARS[47]是另一個基於GUI的MIPS仿真器,設計用於教育,特別是與Hennessy的《電腦組織和設計》一起使用。

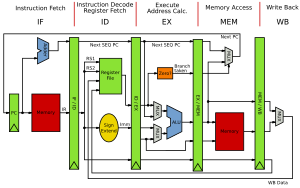

WebMIPS[48]是一個基於瀏覽器的MIPS模擬器,具有通用管線處理器的視覺化表示。該模擬器對於逐步執行期間的暫存器跟蹤非常有用。

QtMips[49][50][51]為基礎電腦架構課程提供簡單的5階段管道視覺化以及快取原理視覺化。提供Windows、Linux、macOS和線上版本。

GXemul(以前稱為mips64emul專案)和QEMU專案提供了更進階的免費模擬器。除了使用它們的整個電腦系統之外,它們還類比各種MIPS III和IV微處理器。

商業模擬器特別適用於MIPS處理器的嵌入式使用,例如Wind River Simics(MIPS 4Kc和5Kc、PMC RM9000、QED RM7000、Broadcom/Netlogic ec4400、Cavium Octeon I)、Imperas(所有MIPS32和MIPS64核心)、VaST系統(R3000、R4000)和CoWare(MIPS4KE、MIPS24K、MIPS25Kf和MIPS34K)。

WepSIM[52]是一個基於瀏覽器的模擬器,其中MIPS指令的子集是微編程的。該模擬器對於學習CPU的工作方式(微編程、MIPS常式、陷阱、中斷、系統呼叫等)非常有用。

參見

參考文獻

- ↑ Patterson, David. Computer Organization and Design. http://booksite.elsevier.com/9780124077263/downloads/historial%20perspectives/section_4.16.pdf: Elsevier. 2014: 4.16–4. ISBN 978-0-12-407726-3.

- ↑ Price, Charles (September 1995). MIPS IV Instruction Set (Revision 3.2), MIPS Technologies, Inc.

- ↑ 3.0 3.1 3.2 3.3 3.4 3.5 3.6 3.7 Sweetman, Dominic. See MIPS Run. Morgan Kaufmann Publishers, Inc. 1999. ISBN 1-55860-410-3.

- ↑ MIPS32 Architecture. MIPS. [2020-03-20].

- ↑ MIPS64 Architecture. MIPS. [2020-03-20].

- ↑ MIPS-3D ASE. Imagination Technologies. [2014-01-04].

- ↑ MIPS16e. MIPS. [2020-03-20].

- ↑ MIPS Multithreading. MIPS. [2020-03-20].

- ↑ University of California, Davis. ECS 142 (Compilers) References & Tools page. [2009-05-28].

- ↑ Turley, Jim. Wait, What? MIPS Becomes RISC-V. Electronic Engineering Journal. 2021-03-08 [2021-03-28].

- ↑ Silicon Graphics Introduces Enhanced MIPS Architecture to Lead the Interactive Digital Revolution. SGI. 1996-10-21.

- ↑ 12.0 12.1 Gwennap, Linley. Digital, MIPS Add Multimedia Extensions (PDF). Microprocessor Report. 1996-11-18, 10 (15): 24–28.

- ↑ Silicon Graphics Previews New High-Performance MIPS Microprocessor Roadmap (新聞稿). 1997-05-12.

- ↑ 14.0 14.1 14.2 14.3 14.4 MIPS Technologies, Inc. Enhances Architecture to Support Growing Need for IP Re-Use and Integration (新聞稿). Business Wire. 1999-05-03.

- ↑ Latest Release of MIPS Architecture Includes Virtualization and SIMD Key Functionality for Enabling Next Generation of MIPS-Based Products (新聞稿). MIPS科技. 2012-12-06.

- ↑ MIPS skips Release 4 amid bidding war. EE Times. 2012-12-10.

- ↑ 存档副本. [2020-07-29].

- ↑ Wave Computing Extends AI Lead by Targeting Edge of Cloud Through Acquisition of MIPS. 2018-06-15.

- ↑ Wave Computing® Launches the MIPS Open Initiative To Accelerate Innovation for the Renowned MIPS® Architecture. 2018-12-17.

- ↑ MIPS Processor ISA To Be Open-Sourced In 2019 - Phoronix.

- ↑ Yoshida, Junko. MIPS Goes Open Source. EE Times. 2018-12-17.

- ↑ MIPS R6 Architecture Now Available for Open Use. 2019-03-28.

- ↑ Wave Computing Closes Its MIPS Open Initiative with Immediate Effect, Zero Warning. 2019-11-15.

- ↑ MIPS becomes RISC-V March 8, 2021. Retrieved March 11, 2021.

- ↑ Wave Computing and MIPS emerge from chapter 11 bankruptcy March 1, 2021. Retrieved March 11, 2021.

- ↑ MIPS R3000 Instruction Set Summary. [2013-08-21].

- ↑ MIPS Instruction Reference. [2013-08-21].

- ↑ MIPS – Market-leading RISC CPU IP processor solutions. imgtec.com. [2016-02-11].

- ↑ Silicon Graphics Introduces Compact MIPS RISC Microprocessor Code For High Performance at a Low Cost (新聞稿). 1996-10-21.

- ↑ Sweetman, Dominic. See MIPS Run 2nd. San Francisco, California: Morgan Kaufmann Publishers. 2007: 425–427. ISBN 978-0-12-088421-6.

- ↑ Using the GNU Compiler Collection (GCC): MIPS DSP Built-in Functions. gcc.gnu.org.

- ↑ Instruction Set Architecture - LinuxMIPS. www.linux-mips.org.

- ↑ Sweetman, Dominic. See MIPS Run, 2nd edition. Morgan Kaufmann. 2007. ISBN 978-0-12088-421-6.

- ↑ MIPS32 Instruction Set Quick Reference.

- ↑ 35.0 35.1 MIPS ABI History.

- ↑ Eric Christopher. mips eabi documentation. binutils@sources.redhat.com (郵寄清單). 2003-06-11 [2020-06-19].

- ↑ NUBI.

- ↑ Karen Miller. "The MIPS Register Usage Conventions". 2006.

- ↑ Hal Perkins. ""MIPS Calling Convention". 2006.

- ↑ MIPSpro N32 ABI Handbook (PDF). Silicon Graphics.

- ↑ PIC code – LinuxMIPS. www.linux-mips.org. [2018-09-21] (英語).

- ↑ System V Application Binary Interface MIPS RISC Processor Supplement, 3rd Edition (PDF): 3–12.

- ↑ Rubio, Victor P. A FPGA Implementation of a MIPS RISC Processor for Computer Architecture Education (PDF). 新墨西哥州立大學. [2011-12-22].

- ↑ OVP: Fast Simulation, Free Open Source Models. Virtual Platforms for software development. Ovpworld.org. [2012-05-30].

- ↑ Imperas. Imperas. 2008-03-03 [2012-05-30].

- ↑ EduMIPS64. Edumips.org. [2012-05-30].

- ↑ MARS MIPS simulator - Missouri State University. Courses.missouristate.edu. [2012-05-30].

- ↑ WebMIPS - MIPS CPU PIPLINED SIMULATION On Line. [2012-01-13].(線上版本),Archived copy. [2012-01-13].(原始碼)

- ↑ QtMips - MIPS CPU simulator for education purposes. [2021-01-24].

- ↑ Kočí, Karel. Graphical CPU Simulator with Cache Visualization (PDF) (學位論文). 布拉格捷克理工大學. 2018 [2021-01-25].

- ↑ Gizopoulos, Dimitris. The basics of QtMips-v3 (PDF). 雅典大學. 2020-12-06 [2021-01-25].

- ↑ WepSim. [2019-08-21]. (Web version with examples). WepSim. [2019-08-21]. (GitHub site with source).

擴充閱讀

- Farquhar, Erin; Philip Bunce. MIPS Programmer's Handbook. Morgan Kaufmann Publishers. 1994. ISBN 1-55860-297-6.

- Patterson, David A; John L. Hennessy. Computer Organization and Design: The Hardware/Software Interface. Morgan Kaufmann Publishers. 2004. ISBN 1-55860-604-1.

- Sweetman, Dominic. See MIPS Run. Morgan Kaufmann Publishers. 1999. ISBN 1-55860-410-3.

- Sweetman, Dominic. See MIPS Run, 2nd edition. Morgan Kaufmann Publishers. 2007. ISBN 978-0-12-088421-6.

外部連結

- MIPS處理器

- prpl基金會(由Imagination Technologies創立的一個支援MIPS平台的非盈利基金會)

- 線上MIPS模擬器

- MIPS Instructions - MIPS Instruction Set

- 計算機組織:MIPS 指令集 (一) 暫存器說明